# STUDY AND SIMULATION OF SIMPLIFIED SPACE VECTOR MODULATION TECHNIQUE FOR THREE LEVEL CASCADED H-BRIDGE INVERTER.

Manasi Ahirrao<sup>1</sup>, M.J.Katira<sup>2</sup>

<sup>1</sup>Student M.Tech, Department of Electrical Engineering, G.H.Raisoni Institute of Engineering and Technology for Women, Nagpur

<sup>2</sup>H.O.D., Department of Electrical Engineering, G.H.Raisoni Institute of Engineering and Technology for Women, Nagpur

1 manasideore 1 @ gmail.com, Cell-8380085992 2 manish.katira@raisoni.net, Cell-8149033427

Abstract – Space vector modulation (SVM) is one of the most favored real-time modulation technique and is most popular due to its digital control pertaining to voltage source inverters (VSI). This paper presents study and simulation of new simplified Space-Vector Pulse Width Modulation (SVPWM) technique for three-level cascaded h-bridge inverter. This technique resembles on to simplify the Space-vector diagram (SVD) of the three level inverter into a two-level inverter. If followed the intended method, the remaining procedures which are required for threelevel SVPWM remains the same as prepared like a conventional two-level inverter and the time required for the execution is tremendously reduced. This method can be implemented to any multilevel inverters above three-level. Simulation results are presented for three-level inverter using three phase load to analyze the system model.

Index Terms—Space Vector Modulation, Space Vector PWM, Cascaded H-bridge, Voltage Source Inverters.

### I. INTRODUCTION

In recent years, multilevel inverters have proven their best ability over the conventional two-level Voltage Source Inverters (VSI). This advancement started from 1981 [3] and it is still booming with great results in the current market. The advantages offered by multilevel inverters over conventional two-level voltage source

inverters includes the reduction in the harmonic content of the output voltage, reduced dv/dt stress on the power electronic devices, switching frequency is reduced, lower device ratings and many more. Multilevel inverts are basically used for high voltage and medium power applications in order to produce improved quality waveforms. An array arrangement of power semiconductors and the capacitor voltage sources in multilevel inverter leads to generate waveforms. voltages with stepping Market applications such as motor drives, renewable or conventional energy generation and distribution, power conditioning devices are implemented with the help of multilevel inverters. There are three different types of multilevel inverters like cascaded H-Bridge, flying capacitor, and diode clamped multilevel inverter. Out of which Cascaded H-Bridge (CHB) has found to be the most advantageous for the above applications [1, 4] because of its modularity, reliability and capability to operate at lower power cells. There are two types of modulation control techniques which are frequently used for the multilevel inverters are carrier-based sinusoidal pulse-width modulation (SPWM) and the Space-Vector Modulation (SVM) techniques [4, 5]. Out of these two, SPWM techniques are simple and easy to implement and it gives approximately identical results as far as the Total Harmonic Distortion (THD) in the output is considered. On the contrary SVM technique, gives more pure and fundamental sinusoidal output voltage. Therefore, SVM continuous is to be

the well-known option for the industrial applications. The complete description of SVM of a two-level VSI is given in [1]. If we go on exceeding the number of levels in the multilevel inverter, then this technique becomes more complicated and tedious to produce the desired results [7-21].

#### I. PRINCIPLE OF SPACE VECTOR MODULATION

Space Vector Modulation (SVM) is based on the representation of the three phase measures as vectors into two dimensions (α, β) plane [1].

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} V_{A0} \\ V_{B0} \\ V_{C0} \end{bmatrix}$$

- Basically, sinusoidal voltage is treated as the constant amplitude vector rotating near to its constant frequency in two dimensions  $(\alpha, \beta)$  plane.

- The reference voltage Vref is approximated using this technique by a combination of the eight switching arrangement's (V0 to V7)

- The reference vector magnitude can be established and utilized to regulate or fine tune the inverter output from these two-phase elements.

- The space-vector s from (V1 to V6) are called as active vectors as they produce the non-zero output voltage whereas the space-vector s V0 and V7 are called as zero vectors as they produce zero output voltage.

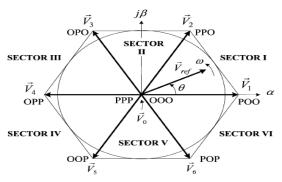

- The Active and zero switching events can be efficiently illustrated through active and zero-space vectors, respectively. A regular space-vector perspective towards the two-level inverter is as represented in Fig.-1, where the 6 active vectors V1 toV6 form a regular-hexagon with 6 equal sectors (I to VI). The zero vector.

Fig-1 Space-vector diagram - Two-level inverter. Source-High-power Converters and AC Drives, IEEE Press, New Jersey, 2006.

#### II. DWELL TIME CALCULATION

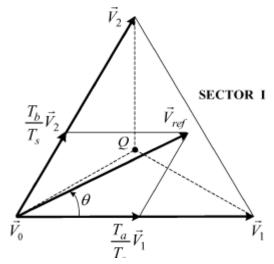

The reference Vref can be incorporated by three stationary sectors. The dwell time for a stationaryvectors basically shows the duty-cycle time (on state or off state) of the selected switches while a sampling period Ts of the modulation scheme. The dwell time calculation depends on 'volt-second balancing' principle, i.e the product about the reference voltage Vref and Ts as the sampling period equates the totality of voltage multiplied with the time intermission concerning to the selected space-vectors. Assuming that the sampling period Ts is sufficiently small, the reference vector Vref can be assumed as the constant during Ts. Under this assumption, Vref can be approximated by the 2 adjacent side active vectors and one zero vector [1].

Fig-2.Vrefsynthesized by V1, V2 and V0. Source-High-power Converters and AC Drives, IEEE Press, New Jersey, 2006

The volt-second balancing equation for this sector is given by

$$Vref2 Ts = V1 Ta + V2 Tb + V0 T0$$

(1)

Where Ts is the time of sampling and Ta, Tb and T0 are the respective dwell times for the vectors V1, V2 and V0. The values of Ta, Tb and T0 are given below [1]:

$$Ta = Ts \times ma \times \sin (\Pi/3 - \theta 2)$$

$$(2)$$

$$Tb = Ts \times ma \times \sin \theta 2$$

$$T0 = Ts - Ta - Tb \tag{4}$$

(3)

Where ma = modulation index, defined as -

$$ma = \sqrt{3} \times V \text{ ref 2} / E$$

(5)

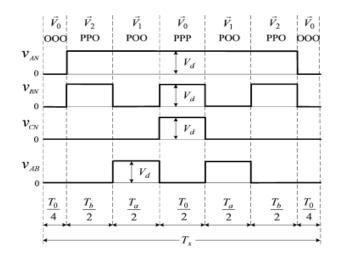

Here after an appropriate switching sequence has to be designed. The typical seven segment switching sequence is used in this technique. The switching order has to be designed by considering the constraint that only one switch should be kept on at one time such that the change through one switching position that goes to the next should involve one inverter leg only and the change from one sector to the next should involve zero or minimum number of swapping [1].

#### III. SWITCHING SEQUENCE

With the space-vectors selected and their corresponding dwell times are calculated and next step is to put an order of switching steps. In general, the switching order design for a given Vref is not singular, but it should fulfill the below two requirements

towards the switching frequency reduction of the device as [1]:

- (a) The transformation from one position switching goes to the next, which involves two switching's in the similar type of inverters, one is being switched on and the other one is off.

- (b) The transition of Vref moving about one sector in the space- vector diagram (SVD) to the next needs minimum number or negligible swapping [1].

Figure 3 shows a seven-segment switching order and output of the inverter

Fig-3. Seven-segment switching order for Vref in sector I.

Source-High-power Converters and AC Drives, IEEE

Press, New Jersey, 2006.

## IV. SIMPLIFIED SPACE VECTOR PWM METHOD FOR A THREE LEVEL INVERTER

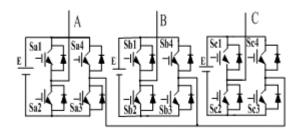

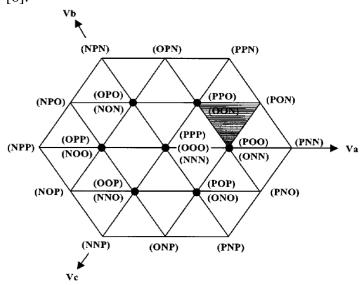

Fig-4 as shown below is the three level cascaded H-bridge inverter. For the three level inverter, three types of switching state-P, O and N in every phase, therefore there exist twenty-seven switching states within three-phase three-level inverter by using the three level inverter space-vector diagram, the basic principle of the explained SVPWM method could be perhaps easily achieved [6]. Switching states of every phase of inverter are listed in table-2.

Fig-4. Three level cascaded H-bridge inverter.

| Switching | Switching States |     |     |     | Terminal |

|-----------|------------------|-----|-----|-----|----------|

| Symbols   | S1X              | S2X | S3X | S4X | Voltage  |

| P         | ON               | ON  | OFF | OFF | VDC/2    |

| O         | OFF              | ON  | ON  | OFF | 0        |

| N         | OFF              | OFF | ON  | ON  | -VDC/2   |

Table-2 Switching states and terminal voltages of the three level inverter.

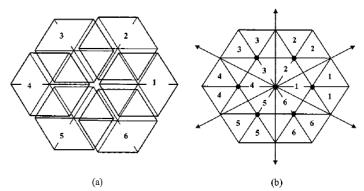

The space-vector diagram (SVD) of the three level inverter as shown in figure-4 which is made up of 6 small hexagons that are shown in the space-vector diagrams (SVD) of the conventional two-level inverters. Each of these six hexagons which constitutes the space-vector diagram (SVD) of the three level inverter, midpoints on the 6 high points of the inner small hexagons which is shown in the figure-6. Therefore by shifting these 6 small hexagons towards the center of inner hexagon by Vdc/3, the space-vector diagram (SVD) of the three level inverter has been simplified like a two-level inverter. To simplify the three level space-vector diagrams into the two-level space-vector diagram as explained above, the following two steps have to be taken.

- 1. Among the 6 hexagons one hexagon is selected within the position of the obtained reference voltage [6].

- 2. Original reference voltage-vector (Vref) has to be deducted by measure from center voltage vector about the specified hexagon [6].

By following the above two steps, the three level space-vector diagram is transformed to a two-level space-vector diagram. Then the switching order determination and the calculation of voltage vector duration time are done as the conventional SVPWM method of two-level. As the recommended SVPWM method is same in principle of conventional two-level SVPWM, various techniques used in two-level

SVPWM can be applied to this proposed method too [6].

Fig-4. Space-vector diagram of the three level inverter. Source- [6].

Fig-5 Simplification of a three-level space-vector diagram.

Source- [6].

#### V. SIMULATION RESULTS

Simulation results have been taken for MODULATION INDEX ma=1,sampling timeTs = 1/Fs ,Fs is the sampling frequency that is taken to be 2.1khz and the input voltage (E) is applied to be 200volts.

(a)

(b)

Fig – 6. Test results of the explained SVPWM method with RL load. (a) Line to ground voltage for three-level inverter. (b) Line to line voltage for three-level inverter.

#### VI. CONCLUSION

The SVM technique has been presented for three level inverter. Calculation of dwelling times for voltage vectors have been conducted same as the two-level SVPWM. Thus the explained method minimizes the processing time of three-level SVPWM. This technique can be implemented to the multi-level SVPWM method above three-level. The effectiveness of the presented SVPWM method is demonstrated and verified by experimental results.

#### ACKNOWLEDGMENT

I would like to express my sincere gratitude to my project guide Prof. M. J. Katira (HOD). I am thankful to Mr.Irfan Ahmed, research scholar, VNIT Nagpur for sharing his valuable time and guidance. I would also like to give my thanks to my husband Mr.Prashant Deore and my family who always stood firmly behind

#### REFERENCES

- [1] Wu, B.: 'High-power converters and ac drives' (IEEE Press,2006)

- [2] Irfan Ahmed, Vijay B. Borghate. 'Simplified space vector modulation technique for seven-level cascaded H-bridge inverter', IET Power Electron., 2014, Vol. 7, Iss. 3, pp. 604–613, doi: 10..1049/iet-pel.2013.013

- [3] Nabae, A., Takahashi, I., Akagi, H.: 'A new neutral-point clamped PWM inverter', IEEE Trans. Ind. Appl., 1981, IA-17, (5), pp. 518–523

- [4] Rodriguez, J., Lai, J., Peng, F.Z.: 'Multilevel inverters: a survey of topologies, controls, and applications', IEEE Trans. Ind. Electron., 2002, 49, (4), pp. 724–738

- [5] Kouro, S., Malinowski, M., Gopakumar, K., et al.: 'Recent advances and industrial applications of multilevel converters', IEEE Trans. Ind. Electron., 2010, 57, (8), pp. 2553–2580

- [6] Jae Hyeong Seo, 'A new simplified space-vector PWM Method for three-level inverters' in IEEE Transactions on power electronics, Vol.16, No.4, July 2001.

- [7] Wei, S., Wu, B., Li, F., Liu, C.: 'A general space vector PWM control algorithm for multilevel inverters'. Proc. 18th Annual IEEE APEC, 2003, vol. 1, pp. 562–568

- [8] Zhang, H., Jouanne, A., Dai, S., Wallace, A.K., Wang, F.: 'Multilevel inverter modulation schemes to eliminate common-mode voltages', IEEE Trans. Ind. Appl., 2000, 36, (6), pp. 1645–1653

- [9] Celanovic, N., Boroyevich, D.: 'A fast space vector modulation algorithm for multilevel three-phase converters', IEEE Trans. Ind. Appl., 2001, 37, (2), pp. 637–641

- [10] Massoud, A.M., Finney, S.J., Cruden, A., Williams, B.W.: 'Mapped phase-shifted space vector modulation for multilevel voltage-source inverters', IET Electr. Power Appl., 2007, 1, (4), pp. 622–636

- [11] Massoud, A.M., Finney, S.J., Williams, B.W.: 'Mapped hybrid spaced vector modulation for multilevel cascaded-type voltage source inverters', IET Power Electron., 2008, 1, (3), pp. 318–335

- [12] Adam, G.P., Finney, S.J., Ojo, O., Williams, B.W.: 'Quasitwo-level and three-level operation of a diode-clamped multilevel inverter using space vector modulation', IET Power Electron., 2012, 5, (5), pp. 542-551

- [13] Gopinath, A., Mohamed, A.S.A., Baiju, M.R.: 'Fractal based space vector PWM for multilevel inverters A novel approach', IEEE Trans. Ind. Electron., 2009, 56, (4), pp. 1230–1237

- [14] Mohamed, A.S.A., Gopinath, A., Baiju, M.R.: 'A simple space vector PWM generation scheme for any general n-level inverter', IEEE Trans. Ind. Electron., 2009, 56, (5), pp. 1649–1656

- [15] Gupta, A.K., Khambadkone, A.M.: 'A space vector PWM scheme for multilevel inverters based on two-level space vector PWM', IEEE Trans. Ind. Electron., 2006, 53, (5), pp. 1631–1639

- [16] Wu, F.J., Zhao, K., Sun, L.: 'Simplified multilevel space vector pulse width modulation scheme based on two-level space vector pulse-width modulation', IET Power Electron., 2012, 5, (5), pp. 609–616

- [17] McGrath, B.P., Holmes, D.G., Lipo, T.A.: 'Optimized space vector switching sequences for multilevel inverters', IEEE Trans. Power Electron., 2003, 18, (6), pp. 1239–1301

- [18] SurendraBabu, N.N.V., Fernandes, B.G.: 'Cascaded two-level inverter-based multilevel static VAr compensator using 12-sided polygonal voltage space vector modulation', IET Power Electron., 2012, 5, (8), pp. 1500–1509

- [19] Naumanen, V., Luukko, J., Itkonen, T., Pyrhonen, O., Pyrhonen, J.: 'Modulation technique for series-connected Hbridge multilevel converters with equal load sharing', IET Power Electron., 2009, 2, (3), pp. 275–286

- [20] Renge, M.M., Suryawanshi, H.M.: 'Five-level diode clamped inverter to eliminate common mode voltage and reduce dv/dt in medium voltage rating induction motor drives', IEEE Trans. Power Electron., 2008, 23, (4), pp. 1598–1607

- [21] Abdul Kadir, M.N., Mekhilef, S., Ping, H.W.: 'Voltage vector control of a hybrid three-stage 18-level inverter by vector decomposition', IET Power Electron., 2010, 3, (4), pp. 601–611

- [22] Houldsworth, J.A., Grant, D.A.: 'The use of harmonic distortion to increase the output voltage of a three-phase PWM inverter', IEEE Trans. Ind. Appl., 1984, IA-20, (5), pp. 1224–1228